While looking around tentative projects, I am looking for clarify something for the project “ADD SUPPORT TO MIPS”, I’ve previously worked on a MIPS-inspired dual-core architecture with a FreeRTOS port, handling things like shared L1 cache, round-robin memory arbiters, and dual-core task scheduling. I wanted to clarify whether we are focusing strictly on the OS-level enablement (CPU hooks, IPIs, and BSP updates) for the standard MIPS ISA, and if we have to simulate it preferably on QEMU, right?

Yes, the project would focus on the OS-level enablement. It would be preferable to test it in a simulator for ease of collaboration and maintenance.

I’ve been working on setting up the environment for the MIPS Malta SMP project and wanted to share some progress.

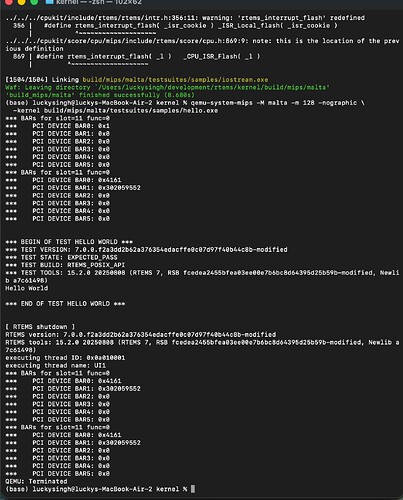

I first Successfully built and configured the mips-rtems7 toolchain on my macOS. After resolving some header conflicts in RTEMS 7, I managed to successfully build the kernel (1504/1504 tasks). I have successfully booted the hello.exe sample on the Malta BSP using QEMU.

I identified a conflict between cpukit/score/cpu/mips/include/rtems/score/cpu.h and generic RTEMS headers regarding interrupt macros. I’ve temporarily bypassed this with -Wno-error but am preparing a proper #ifndef patch to fix this upstream.

The default BSP was crashing due to uninitialized TLB mapping for USEG memory. I modify the linker script to shift the RAM ORIGIN to 0x80000000 (KSEG0/Unmapped Physical). This confirmed that the core kernel and serial drivers are functional.

Solution of Header conflict bug.

cat > config.ini << EOF

[mips/malta]

RTEMS_POSIX_API = True

RTEMS_SMP = False

OPTIMIZATION_FLAGS = -O0 -g

WARNING_FLAGS = -Wno-error

LDFLAGS = -Wl,–defsym,RAM_START=0x80000000

EOF

This is a good start and should be enough for you to begin to work on your proposal. Do feel free to continue the conversation here as well.

I wanted to give some updates about the progress . I’ve successfully resolved the build blockers and achieved core isolation in the early boot stage.

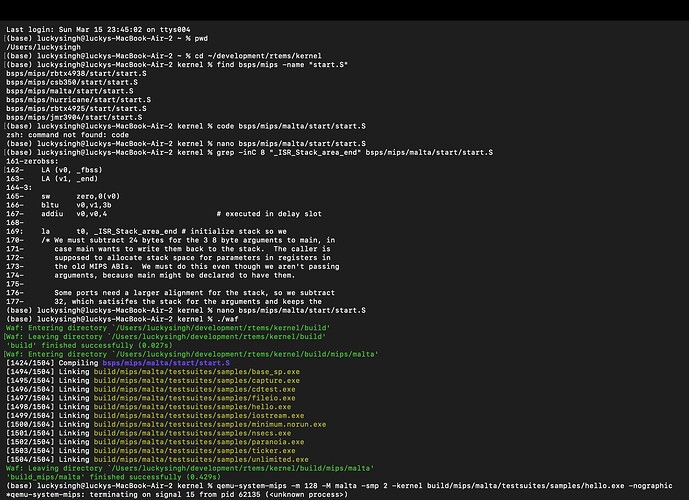

I first updated the spinlock logic in cpu.c to use native MIPS ll/sc (Load Linked / Store Conditional) instructions. This was necessary to properly handle atomic exchanges and resolve C11 _Atomic type mismatches. then I cleaned up cpuimpl.h by removing redundant function declarations. This resolved the “multiple definition” linker errors that were previously creating errors in the build process. After that I implemented logic to read the CP0 EBase register (Register 15, Select 1) to accurately identify the CPU ID (Core 0 vs Core 1) at the very start of the boot process. I added a branch to ensure that only the primary processor (Core 0) executes the .bss zeroing loop. This prevents race conditions where both cores might attempt to clear memory simultaneously. Based on the CPU ID, I implemented a stack offset calculation. Each core now calculates its unique stack area starting from _ISR_Stack_area_end, ensuring that Core 0 and Core 1 have completely isolated stacks. I added a secondary_park loop using a wait instruction. This “parks” the secondary core in an idle state, allowing Core 0 to proceed to boot_card without interference.

Now for validating and debugging I used qemu

The kernel now builds successfully

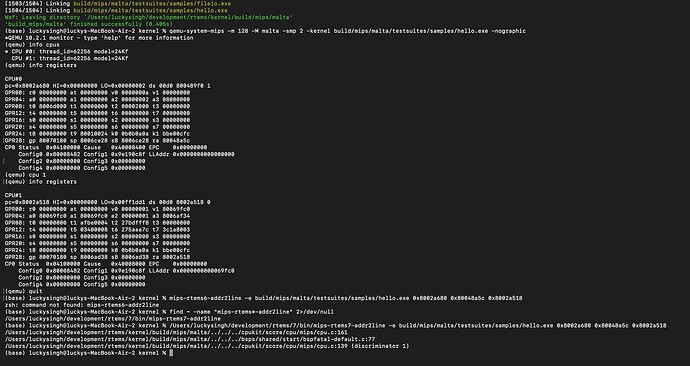

I verified the implementation (-smp 2) using the monitor to inspect registers.

Using addr2line, I confirmed that both cores have successfully entered the C environment:

Core 0 reached bspfatal-default.c:77 (Fatal halt at cpu.c:161), which confirms the primary boot path is active. Core 1 is successfully isolated at cpu.c:139, confirming the assembly-level branching and parking logic works.

I would appreciate any suggestions or guidance by the community.

Since the atomic fixes and early boot intialization are now working and tested on qemu, would you recomment that I submit this progress as MR ? Also, Now I’m looking forward to implement the wake-up call to core 1 and then implement the inter-processor interrupts and synchronisation. I would highly appreciate any suggestions by mentors and community.

Yes, you could submit an MR for the interim progress. At this point you should be focused on writing your proposal.

Sure I will submit the MR for the interim progress soon. I also noticed that you @gedare and @JoelSherrill are listed as mentors for this project, please let me know if there are any updates regarding the same. Also, may I reach out to the respective mentors to get my proposal reviewed?